Mastering Digital Circuit Design with VHDL: A Comprehensive Guide

Introduction: VHDL (VHSIC Hardware Description Language) is a powerful hardware description language widely used for designing and modeling digital circuits and systems. Originally developed for the U.S. Department of Defense in the 1980s, VHDL has become an industry-standard language for digital design, verification, and synthesis in the field of electronic engineering. In this comprehensive guide, we will delve into the process of programming in VHDL for digital circuit design, covering key concepts, modeling techniques, design methodologies, and best practices to help engineers master the art of digital design using VHDL.

Section 1: Understanding VHDL Programming

1.1 Importance of VHDL in Digital Design: VHDL plays a critical role in digital circuit design, providing a systematic and structured approach to describe, model, and simulate digital systems at various levels of abstraction. VHDL enables engineers to specify hardware behavior, functionality, and interconnections using a textual representation, facilitating design exploration, analysis, and implementation of complex digital circuits and systems.

1.2 Overview of VHDL Language: VHDL is a hardware description language used to describe the structure, behavior, and functionality of digital circuits and systems. It provides constructs for describing entities, architectures, signals, processes, and concurrent statements, allowing engineers to model digital designs hierarchically, modularity, and scalability. VHDL supports behavioral, dataflow, and structural modeling styles, making it suitable for diverse applications in digital design, verification, and synthesis.

Section 2: Getting Started with VHDL Programming

2.1 VHDL Syntax and Structure: Learn the syntax and structure of VHDL language, including keywords, identifiers, data types, operators, and language constructs used to define entities, architectures, and components in VHDL code. Understand the hierarchical structure of VHDL designs, including entity declarations, architecture bodies, signal declarations, and process statements, to organize and modularize digital designs effectively.

2.2 Entity-architecture Modeling: Model digital circuits and systems in VHDL using the entity-architecture modeling paradigm, which separates the interface (entity) from the implementation (architecture) of a design. Define entities to specify input/output ports, generic parameters, and internal signals, and describe architectures to specify the behavior, logic, and functionality of a design using concurrent or sequential statements.

2.3 Behavioral Modeling: Use behavioral modeling techniques in VHDL to describe digital system functionality, control, and behavior using process statements, conditional statements, loop statements, and sequential control structures. Model combinatorial logic, sequential logic, state machines, and control algorithms using VHDL behavioral constructs to capture desired system behavior and functionality accurately.

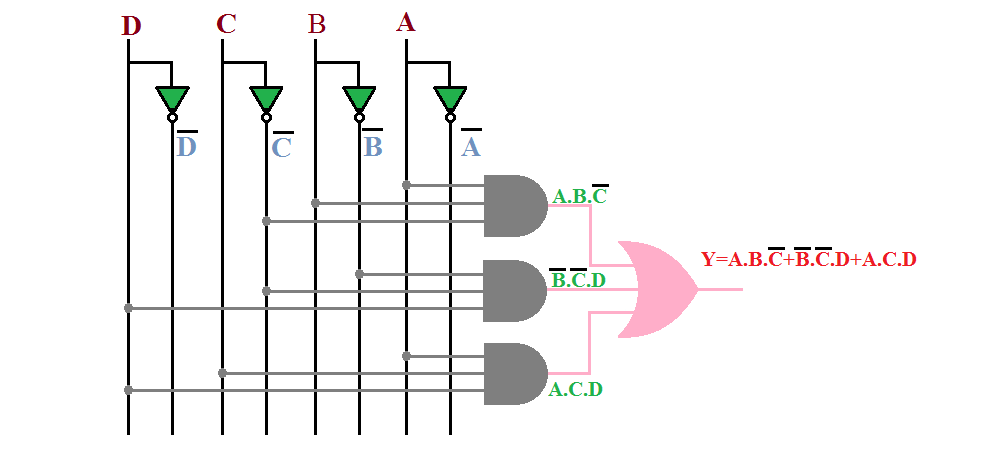

2.4 Dataflow Modeling: Implement dataflow modeling in VHDL to describe digital system functionality, data processing, and signal flow using concurrent assignment statements, signal assignments, and concurrent signal drivers. Model digital circuits as interconnected functional blocks, gates, registers, and multiplexers, specifying signal dependencies and data propagation paths using VHDL dataflow constructs.

Section 3: Advanced VHDL Programming Techniques

3.1 Structural Modeling: Apply structural modeling techniques in VHDL to describe digital system architecture, connectivity, and component composition using component instantiation, port mapping, and interconnection statements. Decompose complex digital designs into modular components, entities, and architectures, and instantiate reusable components to build hierarchical and scalable designs in VHDL.

3.2 Testbench Development: Develop testbenches in VHDL to verify and validate digital designs, simulate circuit behavior, and perform functional verification using test vectors, stimulus generation, and response checking techniques. Model test stimuli, input patterns, and expected outputs using VHDL testbench constructs, including process statements, signal assignments, and assertion statements.

3.3 Synthesis Optimization: Optimize VHDL designs for synthesis targeting programmable logic devices (PLDs), application-specific integrated circuits (ASICs), or field-programmable gate arrays (FPGAs) using synthesis directives, constraints, and optimization techniques. Design for synthesis considerations include timing constraints, clock domain crossing, resource utilization, and design constraints to meet performance, power, and area requirements.

3.4 Design Verification and Debugging: Verify VHDL designs using simulation, formal verification, and debugging techniques to identify and resolve design issues, errors, and functional discrepancies. Use simulation tools, waveform viewers, and debuggers to trace signal paths, monitor state transitions, and validate design correctness against specifications, requirements, and design constraints.

Section 4: Best Practices for VHDL Programming

4.1 Modular Design and Reuse: Adopt modular design principles and design reuse strategies in VHDL to promote design scalability, flexibility, and maintainability. Encapsulate functional blocks, components, and modules into reusable entities, architectures, and libraries, and instantiate them in higher-level designs to facilitate design reuse, modularity, and abstraction.

4.2 Design Documentation and Comments: Document VHDL designs thoroughly using comments, annotations, and design documentation to provide clarity, context, and understanding of design intent, functionality, and implementation details. Include design specifications, requirements, block diagrams, timing diagrams, and interface definitions in design documentation to facilitate collaboration, review, and maintenance.

4.3 Coding Style and Conventions: Follow coding style guidelines and conventions for VHDL programming to ensure code readability, consistency, and portability across different projects and teams. Adopt naming conventions, indentation rules, capitalization styles, and formatting guidelines to enhance code clarity, understandability, and maintainability in VHDL designs.

4.4 Design Validation and Verification: Validate VHDL designs through rigorous testing, verification, and validation processes to ensure design correctness, robustness, and reliability. Perform functional simulation, timing analysis, and formal verification to verify design functionality, performance, and compliance with specifications, standards, and design constraints.

Conclusion: Programming in VHDL for digital circuit design offers engineers a powerful and versatile approach to design, model, and simulate complex digital systems with accuracy and efficiency. By mastering VHDL programming techniques, engineers can leverage the expressive power and flexibility of VHDL language to design innovative digital circuits, optimize system performance, and accelerate product development in diverse applications, from consumer electronics to aerospace systems. With proper training, practice, and adherence to best practices outlined in this guide, engineers can become proficient in VHDL programming and unleash their creativity in digital circuit design and innovation.